所属分类:php教程

运算器能够进行算术运算和逻辑运算。运算器的基本功能是完成对各种数据的加工处理,例如算术四则运算,与、或、求反等逻辑运算,算术和逻辑移位操作,比较数值,变更符号,计算主存地址等。运算器是计算机中处理数据的功能部件,对数据处理主要包括数据的算术运算和逻辑数据的逻辑操作;因此,实现对数据的算术与逻辑运算是运算器的核心功能。

php入门到就业线上直播课:进入学习

API 文档、设计、调试、自动化测试一体化协作工具:点击使用

本教程操作环境:windows7系统、Dell G3电脑。

运算器能够进行算术运算和逻辑运算。

运算器:arithmetic unit,计算机中执行各种算术运算和逻辑运算操作的部件。

运算器由算术逻辑单元(ALU)、累加器、状态寄存器、通用寄存器组等组成。算术逻辑运算单元(ALU)的基本功能为加、减、乘、除四则运算,与、或、非、异或等逻辑操作,以及移位、求补等操作。计算机运行时,运算器的操作和操作种类由控制器决定。运算器处理的数据来自存储器;处理后的结果数据通常送回存储器,或暂时寄存在运算器中。与Control Unit共同组成了CPU的核心部分。

运算器是计算机中处理数据的功能部件。对数据处理主要包括数据的算术运算和逻辑数据的逻辑操作。因此,实现对数据的算术与逻辑运算是运算器的核心功能。

运算器的基本功能是完成对各种数据的加工处理,例如算术四则运算,与、或、求反等逻辑运算,算术和逻辑移位操作,比较数值,变更符号,计算主存地址等。

运算器中的寄存器用于临时保存参加运算的数据和运算的中间结果等。运算器中还要设置相应的部件,用来记录一次运算结果的特征情况,如是否溢出,结果的符号位,结果是否为零等。

运算器的运算

加法器

一位全加器:

Si=Ai⊕Bi⊕CiCi+1=AiBi+(Ai⊕Bi)Ci

延迟运算: 与门、或门 1T;异或门3T

行波进位的补码加法/减法器

当M=0时,B数各位经过0异或保持原数B不变,最低位进位为0,结果就是A与B相加;当M=1时,B数各位经过1异或取反,再结合最低位的进位1,结果就是A+(-B)= A-B

定点乘法

在定点计算机中,两个原码表示的数相乘的运算规则是:乘积的符号位由两数的符号位按异或运算得到,而乘积的数值部分则是两个正数相乘之积。

介于串行乘法器已经被淘汰,下面只介绍并行乘法器。并行乘法器的关键是快速产生n*n个位积,然后对位积进行相加运算产生n+n-1个列和。

并行乘法器:

第一步是并行计算nn个位积,为此需要nn个与门;

第二步是利用n*(n-1)个全加器计算列和。

间接补码乘法运算

由于在计算机内数据是以补码形式存在,必须考虑补码乘法运算中由补码、原码之间简便的互换运算

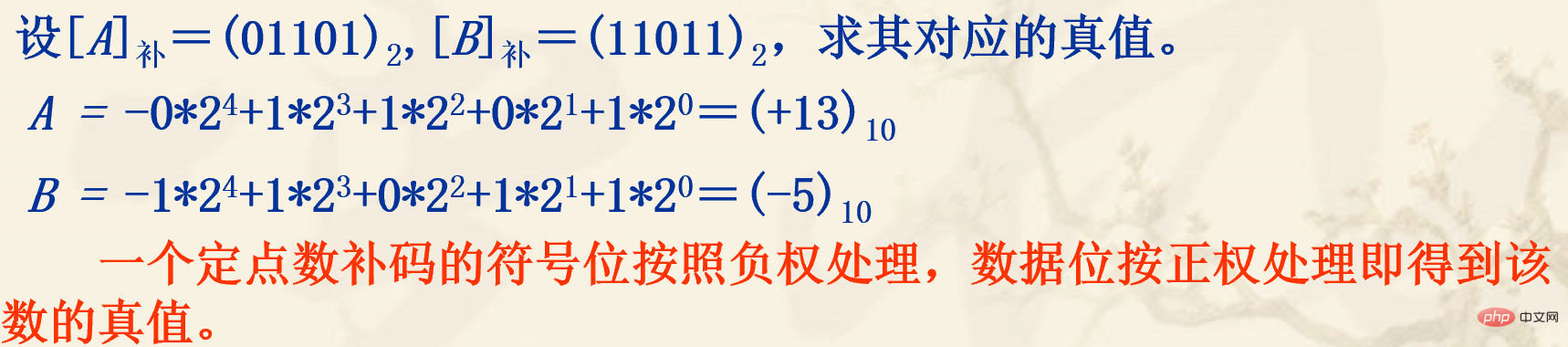

由补码直接求原码的运算:

正数的补码不变,负数的补码等于从右边开始遇到的第一个真值的1以后除了符号位以外1变0,0变1。

求补电路的思想:

如果符号位是0,数据不变

如果符号位是1,则符号位保持不变,数据位从lowbit(x)左边除符号位以外全部求反

串联的或门陆续接受来自低位的数字和上一次的或门输出,一旦某一次低位数字为1,这一次的或门输出及后续的或门输出均为1。每一级的或门输出都会与使能端E相与,当使能端E=1时,简化为直接由或门输出控制。与门输出接异或门,当或门为1,E=1时,异或门发挥求反功能。当使能端为0时,各级异或门均为0,不发挥求反功能,即各位均保持不变。因此,可以将使能端接数的符号位。

间接补码乘法器,即先将两个数经过算前求补器转化为原码,然后经过乘法器,再将结果经过算后求补器转化为补码。

直接补码乘法运算

根据这一特点,我们可以设计输入带有负权的加法器,用来构造直接补码并行乘法器。根据带有负权的输入端数量,可以分为0,1,2,3四类加法器。用混合加法器构造出的并行乘法器如下图:

更多相关知识,请访问常见问题栏目!

以上就是运算器能够进行什么和逻辑运算的详细内容,更多请关注zzsucai.com其它相关文章!